A Comparison of Two Recent Approaches, Exploiting Pipelined FFT and Memory-Based FHT Architectures, for Resource-Efficient Parallel Computation of Real-Data DFT

Abstract

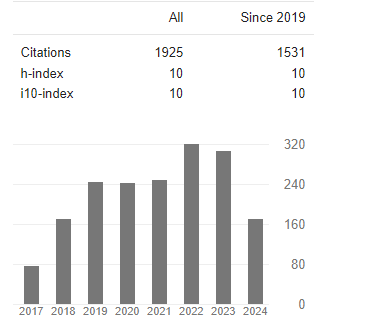

Dr. Keith Jones

This paper provides a comparison and assessment of both the performance and the capabilities of two recently developed approaches to the problem of computing the real-data DFT. The approaches exploit pipelined FFT and memory-based FHT architectures and aim to produce resource-efficient parallel solutions as required for use in resource and power constrained environments. The FFT-based solutions involve multi PE pipelined designs, geared to streaming (or serial) operation, that exploit the conjugate symmetric nature of the real-data DFT spectrum. The FHT based solutions, which are suitably optimized versions of the regularized FHT, are geared to batch (or block-based) operation and involve a memory-based single-PE design that exploits partitioned memory in order to achieve eight fold parallelism within the PE. After outlining the performance objectives of each approach the study highlights the key properties and relative advantages/disadvantages of each, showing how the arithmetic complexity may be traded off against the memory requirement in order to optimize the use of the available silicon resources on the target computing device and to meet the appropriate timing objectives or constraints. A number of additional design issues not addressed with recent real-data FFT research – in particular, those relating to design simplicity, regularity and scalability – are also discussed which enable a more comprehensive assessment of a solution’s capabilities.